The SoC Inflection: How System-on-Chip Design Evolves After 2026

By 2026, system-on-chip design reaches a structural inflection point. The challenge is no longer how many functions can be pulled onto a single die, but how coherently complexity can be distributed without collapsing under verification cost, power density, and design latency. The classical SoC playbook—larger monoliths at newer nodes—continues to exist, but it stops being the dominant path for differentiation. What replaces it is not a single technology shift, but a layered redefinition of what “system” means in silicon.

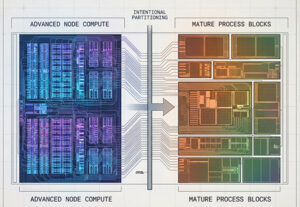

Monolithic Scaling Gives Way to Architectural Selectivity

This asymmetry reshapes SoC floorplanning. Instead of one massive die dominated by routing congestion and power integrity constraints, the system is partitioned along power, frequency, and reliability domains. The “chip” becomes an assembly of intent-driven components rather than a uniform silicon canvas.

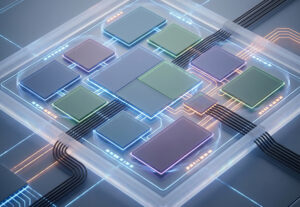

Chipletization Becomes the SoC, Not an Add-On

This forces a shift in design methodology. Architects begin designing for failure isolation, graceful degradation, and upgradeability. A defective or underperforming tile no longer invalidates an entire system. Instead, redundancy and binning strategies are pushed up into the architectural layer, blurring the line between silicon design and system software.

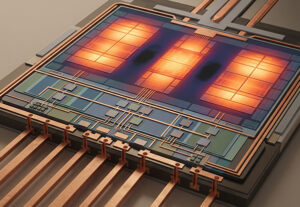

Power Delivery and Thermal Architecture Take Center Stage

Thermal design follows a similar trajectory. Rather than treating heat as a post-layout problem, SoCs are architected with thermal zoning in mind. High-activity tiles are spatially and temporally isolated, workloads are scheduled with thermal awareness, and packaging materials are co-optimized with silicon to maintain predictable operating envelopes.

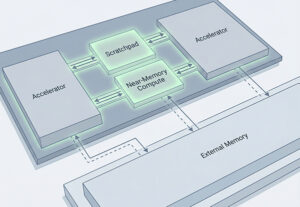

Memory Integration Shifts from Capacity to Proximity

External memory interfaces remain critical, but their role changes. Instead of acting as a universal backing store, off-chip memory becomes a managed resource, accessed through prefetching, compression, and locality-aware scheduling. The SoC’s intelligence increasingly lies in how little data it moves, not how fast it can move everything.

Verification, Not Transistors, Becomes the Bottleneck

This shifts competitive advantage toward organizations that can reuse verified subsystems with strong interface contracts. SoC design becomes less about crafting unique RTL for every generation and more about composing trusted blocks with predictable behavior under defined assumptions.

Software Defines the SoC Boundary

This co-dependence means SoC roadmaps can no longer be planned in isolation. Architectural decisions are evaluated based on how effectively software can exploit, manage, and evolve them over time. Flexibility becomes as valuable as raw performance.

The Post-2026 SoC Identity

After 2026, the SoC is no longer a monolithic artifact frozen at tape-out. It is a modular, power-aware, software-coupled system whose value lies in balance rather than brute force. The most successful designs will not be those that push the hardest on any single metric, but those that harmonize process technology, architecture, packaging, and software into a coherent whole.

The future of SoCs is not about being bigger or faster—it is about being more intentional.