Verification for Tomorrow’s SoCs: Building Confidence from IP to System

The Purpose: Ensuring Real Confidence in Complex Systems

Verification’s real purpose has never been about passing tests.

It’s about building confidence-confidence that when an SoC boots for the first time, the hardware, firmware, and every handshake between IPs behave as intended.

That purpose is now under strain. SoCs have grown into networks of interacting IP blocks: CPU clusters, AI accelerators, coherent fabrics, memory controllers, power islands, security enclaves, and software layers driving them. Each of these may be correct in isolation, yet the overall system can fail because of integration behaviors no single team foresaw.

As Semiconductor Engineering’s “The Future of Verification” notes, verification has become the biggest variable in achieving first-silicon success. The central challenge isn’t writing more tests-it’s proving correctness across interaction boundaries.

The purpose of verification, therefore, must evolve from finding bugs to establishing design trust at every level IP, subsystem, and SoC.

Integration: Where Confidence Is Gained or Lost

Every SoC program begins with verified IP. Each block has its own regression suite, coverage targets, and formal proofs. But when these blocks combine, the rules change.

A PCIe Gen6 controller proven compliant in isolation still faces timing dependencies when connected through a UCIe bridge. A memory controller verified at RTL may misbehave under dynamic voltage scaling commanded by firmware. A coherent interconnect can pass local checks but fail under concurrent cache invalidations triggered by real workloads.

- The recurring pattern is that bugs live in the interactions.

- They arise when two correct modules meet under uncontrolled timing, reset, or power conditions.

Therefore, verification must shift from unit-level completeness to compositional assurance-verifying that components interact safely and predictably under all legitimate system states.

Formal Where It Matters Most

Simulation is statistical-it explores selected behaviors.

Formal verification, though compute-heavy, provides exhaustive certainty for bounded problems.

This makes it ideal for proving properties that define safety and integrity:

- A power-management FSM must never enter an illegal transition sequence.

- A cache controller must never return stale data.

- A security block must never allow secret data on external ports.

When these properties hold formally, confidence rises sharply.

SoC teams increasingly deploy formal tools not everywhere but where failure is unacceptable-clock crossings, reset ordering, security, and coherency.

In one automotive design program, formal proofs replaced hundreds of simulation runs by guaranteeing that a safety monitor’s fault-response timing met ISO-26262 requirements under all modes. That’s not faster testing; it’s deeper assurance, fulfilling the real purpose of verification.

Bringing Reality into the Loop

Confidence doesn’t come from abstraction alone. It also depends on observing the system behave under realistic workloads.

- Emulation and prototyping make this possible.

- A neural-network SoC with tens of billions of transistors cannot be verified in simulation, but it can boot firmware, run models, and train links inside an emulator. Power-cycle tests, firmware recovery routines, and OS initialization sequences can all be validated before tape-out.

- In multi-die environments-where dies communicate via UCIe or proprietary interconnects-this step is crucial.

- It’s not enough to know that protocol packets are legal; verification must confirm that lane retraining, error recovery, and sideband management behave as expected over real-time intervals.

- Emulation enables this by allowing long-duration, system-level verification that captures the kind of issues simulation misses.

The result aligns with the core purpose: proving that what is designed is what will actually work once powered.

Assistance, Not Automation

- There’s increasing enthusiasm for tools that apply analytics or machine learning to verification data. Properly used, they advance the purpose of verification-to make engineering judgment more informed, not replaced.

- A regression analysis tool that clusters similar failures, or a coverage assistant that highlights untested logic, saves effort without diluting responsibility.

- An AI system that proposes assertions from design specifications can accelerate setup, but engineers must still review every property for intent and correctness.

- When managed carefully, these assistants’ free engineers to focus on reasoning rather than repetition-restoring human insight as the core of verification.

Security and the Uninvited State

- Modern SoCs are not only complex-they’re exposed.

- Security blocks, cryptographic IPs, and privilege controls create new attack surfaces.

- Verification now includes adversarial testing through hardware fuzzing-generating unpredictable or malformed inputs that force designs into rarely visited states.

- Research and industry pilots show this method revealing race conditions, leakage paths, and privilege-escalation bugs that escaped formal and simulation efforts.

- The point isn’t to find random errors; it’s to verify robustness under stress, another dimension of confidence. A secure SoC isn’t merely functionally correct-it remains correct even under unintended conditions.

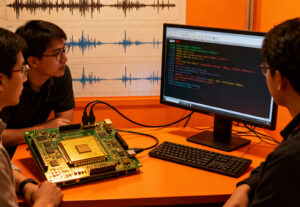

Hardware–Software Convergence

- No SoC functions without firmware and control software. Many failures once attributed to “hardware bugs” are actually mismatches between software timing and hardware state.

- Verification must therefore extend to hardware-software behavior as a whole.

- When a CPU issues a low-power request, or a memory controller performs calibration, both hardware and firmware are active participants.

- By running firmware inside emulation or co-simulation, teams can validate real sequences, timing dependencies, and interrupt handling before silicon.

- This not only prevents latent bugs but ensures that the system behaves correctly in its natural operating environment-the ultimate measure of verification success.

Delivering Confidence as a Product

- For IP and subsystem providers, verification has become a deliverable in itself.

- Customers now expect verification collateral-assertions, testbenches, formal proofs, and coverage reports-alongside RTL.

- When each IP arrives with documented verification evidence, SoC integrators can build on top of a trusted foundation.

- This changes the verification culture: it’s no longer a private activity hidden within teams but part of the product supply chain. Confidence travels with the IP.

Re-Emphasizing the Purpose

Across all these methods-formal proofs, emulation, analytics, fuzzing, and co-verification-the constant theme is confidence through evidence. The purpose of verification is not to collect coverage numbers or regression statistics. It is to create demonstrable, reviewable proof that a design will behave correctly in the field, under real conditions, with all its moving parts interacting.

That purpose must remain explicit in every phase:

- When formal tools prove invariants, they build confidence by removing uncertainty.

- When emulation shows the system booting software, it builds confidence by showing expected behavior.

- When AI tools help identify weaknesses faster, they build confidence by increasing clarity.

- When IP suppliers deliver verification data as part of their handoff, they build confidence through transparency.

Verification is thus no longer a closing phase-it’s a continuous process of confidence building, from IP conception to full SoC validation.

Conclusion: Making Verification Serve Its True Goal

Modern SoCs are too complex to verify by habit. The industry can no longer rely on brute-force simulation or late-stage firefighting. Verification must reclaim its original purpose: to provide dependable evidence that the design works as intended, not just in isolated tests, but as a living system.

That requires a practical blend of formal assurance, realistic system testing, security-aware stress, and intelligent human-guided automation. Each contributes to the same outcome-trust in silicon before silicon exists.

When verification is practiced with that purpose in mind, it stops being a bottleneck and becomes a design strength. It transforms from an activity of checking to an activity of proving, fulfilling its role as the foundation of every successful SoC program.

References

- Semiconductor Engineering – “The Future of Verification” (Sept 2025)

- Siemens EDA / Wilson Research Group – “2024 IC/ASIC Functional Verification Trend Report”

- Cadence – “Palladium Z3 and Protium X3 Emulation Platforms”

- Synopsys – “ZeBu-200 and AI-Enhanced Verification Workflows” (2025)

- Siemens EDA – “UCIe Verification and Multi-Die Validation Challenges,” Verification Horizons (2025)

- Ma et al. – “Bridging the Gap Between Hardware Fuzzing and Industrial Verification,” arXiv (2025)

- Wu et al. – “GenHuzz: White-Box Hardware Fuzzing Using LLMs,” USENIX Security (2025)

- Huang et al. – “Instruction-Level Abstraction (ILA): A Formal Interface for Accelerator Verification”

- OpenTitan Project – “Design Verification Methodology and Coverage Strategy” (2025)